Mountain View in Santa Clara County, California — The American West (Pacific Coastal)

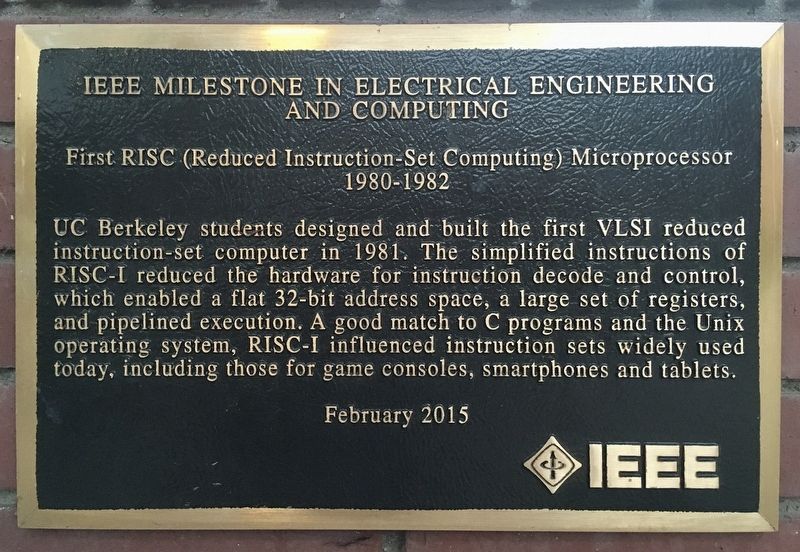

First RISC Microprocessor

Reduced Instruction-Set Computing

— IEEE Milestone in Electrical Engineering and Computing —

Erected 2015 by Institute of Electrical and Electronics Engineers.

Topics and series. This historical marker is listed in these topic lists: Industry & Commerce • Science & Medicine. In addition, it is included in the IEEE Milestones in Electrical Engineering and Computing series list. A significant historical year for this entry is 1981.

Location. 37° 24.886′ N, 122° 4.661′ W. Marker is in Mountain View, California, in Santa Clara County. Marker can be reached from Shoreline Boulevard north of U.S. 101, on the right when traveling north. Located at the Computer History Museum. Touch for map. Marker is at or near this postal address: 1401 N Shoreline Blvd, Mountain View CA 94043, United States of America. Touch for directions.

Other nearby markers. At least 9 other markers are within walking distance of this marker. Online Systems and Personal Computing (here, next to this marker); SPICE (here, next to this marker); DIALOG Online Search System (here, next to this marker); Birthplace of Silicon Valley (here, next to this marker); SPARC RISC Architecture (here, next to this marker); Moore’s Law (here, next to this marker); Shakey: The World's First Mobile Intelligent Robot (here, next to this marker); The Floating Gate EEPROM (here, next to this marker); Computer History Museum (here, next to this marker). Touch for a list and map of all markers in Mountain View.

Credits. This page was last revised on September 28, 2021. It was originally submitted on September 27, 2021, by Craig Baker of Sylmar, California. This page has been viewed 117 times since then and 9 times this year. Photos: 1, 2, 3. submitted on September 27, 2021, by Craig Baker of Sylmar, California.